December 1998

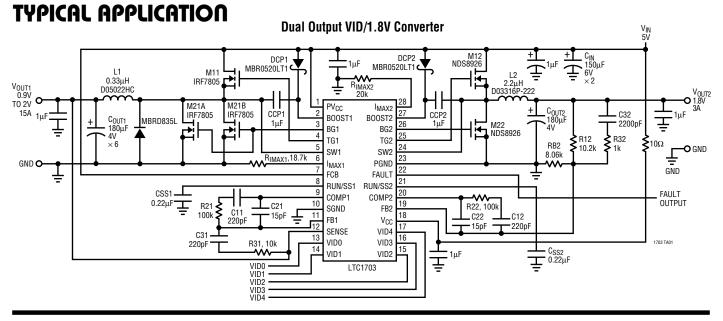

<sup>Y</sup> Dual 550kHz Synchronous 5V-to-2.x/1.xV Switching Regulator Controllers with VID

### FEATURES

- Two Independent Controllers in One Package

- LTC1703 Side 1 Output Is Compliant with the Intel Mobile VID Specification

- Two Sides Run Out-of-Phase to Minimize C<sub>IN</sub>

- All N-Channel External MOSFET Architecture

- No External Current Sense Resistor

- Excellent Output Regulation: 1% Initial Accuracy over Line and Load

- 550kHz Switching Frequency Minimizes External Component Size

- 1A to >20A Output Current per Channel

- ≥90% Efficiency over Wide Load Current Range

- Quiescent Current Drops Below 100µA in Shutdown

- Small SSOP Packages

#### **APPLICATIONS**

- Microprocessor Core/IO Supplies

- Multiple Logic Supply Generator

- Distributed Power Applications

- High Efficiency Power Conversion

**L**, LTC and LT are registered trademarks of Linear Technology Corporation. Burst Mode is a trademark of Linear Technology Corporation.

# DESCRIPTION

The LTC<sup>®</sup>1702/LTC1703 are dual switching regulator controllers optimized for high efficiency with low input voltages. Each includes two complete, independent switching regulator controllers on-chip, designed to drive a pair of external N-channel MOSFET devices in a voltage mode feedback, synchronous buck configuration. The LTC1703 includes digital output voltage adjustment at controller 1 that conforms to the Intel Mobile VID specification. The LTC1702/ LTC1703 use a constant-frequency, true PWM design switching at 550kHz, minimizing external component size and cost and maximizing load transient performance. The synchronous buck architecture automatically shifts to discontinous and then to Burst Mode<sup>™</sup> operation as the output load decreases, ensuring 90% or greater efficiency over a wide range of load currents.

The LTC1702/LTC1703 feature onboard references trimmed to 0.5% and can provide better than 1% regulation at the converter outputs. An optional latching FAULT mode protects the load if the output rises 15% above the intended voltage. Each channel can be enabled independently; with both channels disabled, the LTC1702/LTC1703 shut down and supply current drops below 100µA.

### ABSOLUTE MAXIMUM RATINGS (Note 1)

| Supply Voltage                                       |

|------------------------------------------------------|

| V <sub>CC</sub>                                      |

| BOOST <i>n</i>                                       |

| BOOST <i>n</i> – SW <i>n</i> 7V                      |

| Input Voltage                                        |

| SW <i>n</i>                                          |

| All Other Inputs $-0.3V$ to V <sub>CC</sub> + $0.3V$ |

| Peak Output Current                  |                |

|--------------------------------------|----------------|

| TG <i>n</i> , BG <i>n</i>            | 1A             |

| Operating Temperature Range          | 0°C to 70°C    |

| Junction Temperature                 | 150°C          |

| Storage Temperature Range            | -65°C to 150°C |

| Lead Temperature (Soldering, 10 sec) | 300°C          |

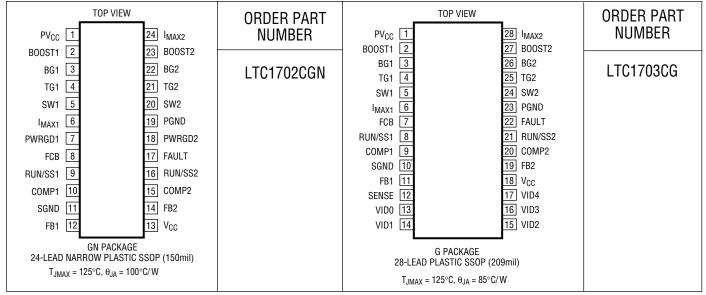

### PACKAGE/ORDER INFORMATION

Consult factory for Industrial and Military grade parts.

#### **ELECTRICAL CHARACTERISTICS** $V_{CC} = 5V$ , $T_A = 25^{\circ}C$ unless otherwise specified. (Note 2)

| SYMBOL             | PARAMETER                        | CONDITIONS                                                                      | MIN   | ТҮР      | MAX   | UNITS    |

|--------------------|----------------------------------|---------------------------------------------------------------------------------|-------|----------|-------|----------|

| Main Contro        | ol Loop                          |                                                                                 |       |          | L     |          |

| V <sub>CC</sub>    | V <sub>CC</sub> Supply Voltage   |                                                                                 |       |          | 7     | V        |

| PV <sub>CC</sub>   | PV <sub>CC</sub> Supply Voltage  | (Note 3)                                                                        |       |          | 7     | V        |

| BV <sub>CC</sub>   | BOOST Pin Voltage                | V <sub>BOOST</sub> – V <sub>SW</sub> (Note 3)                                   |       |          | 7     | V        |

| I <sub>CC</sub>    | V <sub>CC</sub> Supply Current   | RUN/SS1 = RUN/SS2 = V <sub>CC</sub><br>RUN/SS1 = RUN/SS2 = 0V (Note 5)          |       | 6<br>20  |       | mA<br>μA |

| IPV <sub>CC</sub>  | PV <sub>CC</sub> Supply Current  | RUN/SS1 = RUN/SS2 = V <sub>CC</sub> (Note 4)<br>RUN/SS1 = RUN/SS2 = 0V (Note 5) |       | 5<br>20  |       | mA<br>μA |

| I <sub>BOOST</sub> | BOOST Pin Current                | RUN/SS1 = RUN/SS2 = V <sub>CC</sub> (Note 4)<br>RUN/SS1 = RUN/SS2 = 0V (Note 5) |       | 3<br>0.1 |       | mA<br>μA |

| V <sub>FB</sub>    | Feedback Voltage                 | RUN/SS1 = RUN/SS2 = V <sub>CC</sub>                                             | 0.796 | 0.8      | 0.804 | V        |

| $\Delta V_{FB}$    | Feedback Voltage Line Regulation | V <sub>CC</sub> = 2.7V to 7V                                                    |       |          | ±0.5  | %        |

#### **ELECTRICAL CHARACTERISTICS** $V_{CC} = 5V$ , $T_A = 25^{\circ}C$ unless otherwise specified. (Note 2)

| SYMBOL                          | PARAMETER                       | CONDITIONS                                                                                                    | MIN      | ТҮР        | MAX  | UNITS  |

|---------------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------|----------|------------|------|--------|

| I <sub>FB</sub>                 | Feedback Current                |                                                                                                               |          |            | ±1   | μA     |

| $\Delta V_{OUT}$                | Output Voltage Load Regulation  | (Note 6)                                                                                                      |          | 0.1        | ±0.3 | %      |

| V <sub>FCB</sub>                | FCB Threshold                   |                                                                                                               | 0.79     | 0.8        | 0.81 | \<br>\ |

| $\Delta V_{FCB}$                | FCB Feedback Hysteresis         |                                                                                                               |          | 10         |      | m۱     |

| I <sub>FCB</sub>                | FCB Pin Current                 |                                                                                                               |          |            | ±1   | μA     |

| V <sub>RUN</sub>                | RUN Pin Threshold               |                                                                                                               |          | 0.5        |      | V      |

| I <sub>SS</sub>                 | Soft Start Source Current       | RUN/SS <i>n</i> = 0.5V                                                                                        |          | -3         |      | μA     |

| Switching Cha                   | aracteristics                   |                                                                                                               |          |            |      |        |

| fosc                            | Oscillator Frequency            |                                                                                                               | 475      | 550        |      | kHz    |

| $\Phi_{0SC2}$                   | Converter 2 Oscillator Phase    | Relative to Converter 1                                                                                       |          | 180        |      | DEG    |

| DC <sub>MIN1</sub>              | Minimum Duty Cycle              | V <sub>FB</sub> < V <sub>MAX</sub>                                                                            |          | 10         |      | %      |

| DC <sub>MIN2</sub>              | Minimum Duty Cycle              | V <sub>FB</sub> > V <sub>MAX</sub>                                                                            | 0        |            |      | %      |

| DC <sub>MAX</sub>               | Maximum Duty Cycle              |                                                                                                               |          | 90         |      | %      |

| t <sub>NOV</sub>                | Driver Nonoverlap               |                                                                                                               |          | 25         | 100  | ns     |

| t <sub>r</sub> , t <sub>f</sub> | Driver Rise/Fall Time           |                                                                                                               |          | 15         |      | ns     |

| Feedback Am                     | plifier                         |                                                                                                               | -        |            |      |        |

| A <sub>VFB</sub>                | FB DC Gain                      | $C_{L} = 10 pF, R_{L} = 10 k$                                                                                 |          | 65         |      | dE     |

| GBW                             | FB Gain Bandwidth               | $C_{L} = 10 pF, R_{L} = 10 k$                                                                                 |          | 25         |      | MHz    |

| I <sub>FB</sub>                 | FB Sink/Source Current          |                                                                                                               |          | ±10        |      | mA     |

| V <sub>MIN</sub>                | MIN Comparator Threshold        |                                                                                                               |          | 775        |      | m∖     |

| V <sub>MAX</sub>                | MAX Comparator Threshold        |                                                                                                               |          | 825        |      | m∖     |

| Current Limit                   | Loop                            |                                                                                                               | -        |            |      |        |

| A <sub>VL</sub>                 | I <sub>LIM</sub> Gain           |                                                                                                               |          | 35         |      | dB     |

| IIMAX                           | I <sub>MAX</sub> Source Current | I <sub>MAX</sub> = 0V                                                                                         |          | -10        |      | μA     |

| Status Output                   | S                               |                                                                                                               |          |            |      |        |

| V <sub>PWRGD</sub>              | PWRGD Trip Point                |                                                                                                               |          | -3         |      | %      |

| V <sub>OLPG</sub>               | PWRGD Output Low Voltage        | I <sub>PWRGD</sub> = 1mA                                                                                      |          | 0.2        | 0.4  | V      |

| I <sub>PG</sub>                 | PWRGD Output Leakage            |                                                                                                               |          | ±0.1       | ±1   | μA     |

| t <sub>PG</sub>                 | PWRGD Delay Time                |                                                                                                               |          | 100        |      | μ      |

| V <sub>FAULT</sub>              | FAULT Trip Point                |                                                                                                               |          | + 15       |      | %      |

| V <sub>OLF</sub>                | FAULT Output Low Voltage        | I <sub>FAULT</sub> = 1mA                                                                                      |          | 0.2        | 0.4  | V      |

| IFAULT                          | FAULT Output Current            | V <sub>FAULT</sub> = 0V                                                                                       |          | -10        |      | μA     |

| t <sub>FAULT</sub>              | FAULT Delay Time                |                                                                                                               |          | 10         |      | μ      |

| VID Inputs (L                   | C1703 Controller 1 Only)        |                                                                                                               | <u>.</u> |            |      |        |

| R <sub>FB-SENSE</sub>           | Resistance Between SENSE and FB |                                                                                                               |          | 10         |      | kΩ     |

| V <sub>OUT</sub> Error %        | Output Voltage Accuracy         | Programmed from 0.9V to 2V                                                                                    | -0.25    |            | 0.25 | %      |

| R <sub>PULLUP</sub>             | VID Input Pull-Up Resistance    | V <sub>DIODE</sub> = 0.6V (Note 7)                                                                            |          | 40         |      | kΩ     |

| VID <sub>T</sub>                | VID Input Voltage Threshold     | $\begin{array}{c} V_{IL} \ (2.7V \leq V_{CC} \leq 5.5V) \\ V_{IH} \ (2.7V \leq V_{CC} \leq 5.5V) \end{array}$ | 1.6      |            | 0.4  | N<br>N |

| I <sub>VID-LEAK</sub>           | VID Input Leakage Current       | V <sub>CC</sub> < VID < 7V (Note 7)                                                                           |          | 0.01       | ±1   | μA     |

| V <sub>PULLUP</sub>             | VID Pull-Up Voltage             | V <sub>CC</sub> = 3.3V<br>V <sub>CC</sub> = 5V                                                                |          | 2.8<br>4.5 |      | V<br>V |

#### **ELECTRICAL CHARACTERISTICS** $V_{CC} = 5V$ , $T_A = 25^{\circ}C$ unless otherwise specified. (Note 2)

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

**Note 2:** All currents into device pins are positive; all currents out of device pins are negative. All voltages are referenced to ground unless otherwise specified.

**Note 3:**  $PV_{CC}$  and  $BV_{CC}$  ( $V_{BOOST} - V_{SW}$ ) must be greater than  $V_{GS(ON)}$  of the external MOSFETs used to ensure proper operation.

**Note 4:** Supply current in normal operation is dominated by the current needed to charge and discharge the external MOSFET gates and will be higher than the quiescent current drawn by the LTC1702/LTC1703. This current will vary with supply voltage and the external MOSFETs used.

**Note 5:** Supply current in shutdown is dominated by external MOSFET leakage and may be significantly higher than the quiescent current drawn by the LTC1702/LTC1703, especially at elevated temperature. If any of the VID*n* pins are grounded in shutdown, the V<sub>CC</sub> supply current will rise and be approximately equal to the number of grounded VID*n* pins times (V<sub>CC</sub> – 0.6V)/40k.

**Note 6:** This parameter is guaranteed by correlation and is not tested directly.

**Note 7:** Each built-in pull-up resistor attached to the VID inputs also has a senses diode connected to  $V_{CC}$  to allow input voltages higher than the  $V_{CC}$  supply without damage or clamping. (See Applications Information section for further detail.)

#### PIN FUNCTIONS

Note: Pin numbers are listed as (LTC1702 pin/LTC1703 pin)

**PV<sub>CC</sub> (Pin 1/1):** Driver Power Supply Input. PV<sub>CC</sub> provides power to the two BG*n* output drivers. PV<sub>CC</sub> must be connected to a voltage high enough to fully turn on the external MOSFETs M21 and M22. PV<sub>CC</sub> should generally be connected directly to V<sub>IN</sub>. PV<sub>CC</sub> requires at least a 1 $\mu$ F bypass capacitor directly to PGND.

**BOOST1 (Pin 2/2):** Controller 1 Top Gate Driver Supply. The BOOST1 pin supplies power to the floating TG1 driver. BOOST1 should be bypassed to SW1 with a 1 $\mu$ F capacitor. An additional Schottky diode from V<sub>IN</sub> to BOOST1 pin will create a complete floating charge-pumped supply at BOOST1. No other external supplies are required.

**BG1 (Pin 3/3):** Controller 1 Bottom Gate Drive. The BG1 pin drives the gate of the bottom N-channel synchronous switch MOSFET, M21. BG1 is designed to drive up to 10,000pF of gate capacitance directly. If RUN/SS1 goes low, BG1 will go low, turning off M21. If FAULT mode is tripped, BG1 will go high and stay high, keeping M21 on until the power is cycled.

**TG1 (Pin 4/4):** Controller 1 Top Gate Drive. The TG1 pin drives the gate of the top N-channel MOSFET, M11. The TG1 driver draws power from the BOOST1 pin and returns to the SW1 pin, providing true floating drive to M11. TG1 is designed to drive up to 10,000pF of gate capacitance directly. In shutdown or fault modes, TG1 will go low.

**SW1 (Pin 5/5):** Controller 1 Switching Node. SW1 should be connected to the switching node of converter 1. The TG1 driver ground returns to SW1, providing floating gate

drive to the top N-channel MOSFET switch, M11. The voltage at SW1 is compared to  $I_{MAX1}$  by the current limit comparator while the bottom MOSFET, M21, is on.

**I**<sub>MAX1</sub> (Pin 6/6): Controller 1 Current Limit Set. The I<sub>MAX1</sub> pin sets the current limit comparator threshold for controller 1. If the voltage drop across the bottom MOSFET, M21, exceeds the magnitude of the voltage at I<sub>MAX1</sub>, controller 1 will go into current limit. The I<sub>MAX1</sub> pin has an internal 10µA current source pull-up, allowing the current threshold to be set with a single external resistor to PGND.

**PWRGD1 (Pin 7/NA):** Controller 1 Power Good. PWRGD1 is an open-drain logic output. PWRGD1 will pull low whenever  $V_{OUT1}$  falls 3% below its programmed value. When RUN/SS1 is low (side 1 shut down), PWRGD1 will go high. The LTC1703 does not have PWRGD pins.

**FCB (Pin 8/7):** Force Continuous Bar. The FCB pin forces both converters to maintain continuous synchronous operation regardless of load when the voltage at FCB drops below 0.8V. FCB is normally tied to  $V_{CC}$ . To force continuous operation, tie FCB to SGND, FCB can also be connected to a feedback resistor divider from a secondary winding on one converter's inductor to generate a third regulated output voltage.

**RUN/SS1 (Pin 9/8):** Controller 1 Run/Soft Start. Pulling RUN/SS1 to SGND will disable controller 1 and turn off both of its external MOSFET switches. Pulling both RUN/SS pins down will shut down the entire LTC1702, dropping the quiescent supply current to below 100µA. A capacitor from RUN/SS1 to SGND will control the turn-on

#### PIN FUNCTIONS

and rate of rise of the controller 1 output voltage at powerup. An internal  $10\mu$ A current source pull-up at the RUN/SS1 pin sets the turn-on time at approximately 150ms/µF.

**COMP1 (Pin 10/9):** Controller 1 Loop Compensation. The COMP1 pin is connected directly to the output of the first controller's error amplifier and the input to the PWM comparator. An RC network is used at the COMP1 pin to compensate the feedback loop for optimum transient response.

**SGND (Pin 11/10):** Signal Ground. All internal low power circuitry returns to the SGND pin. Connect to a low impedance ground, separated from the PGND node. All feedback, compensation and soft start connections should return to SGND. SGND and PGND should connect only at a single point, near the PGND pin and the negative plate of the  $V_{IN}$  bypass capacitor.

**FB1 (Pin 12/11):** Controller 1 Feedback Input. On the LTC1702, FB1 should be connected through a resistor divider to  $V_{OUT1}$  to set the output voltage. The loop compensation network for controller 1 also connects to FB1. In the LTC1703, FB1 is connected to the internal VID network, and should only be connected to the compensation network.

**SENSE (NA/Pin 12):** Output Sense. Connect to V<sub>OUT1</sub>. The LTC1702 does not include a SENSE pin.

**VID0 to VID4 (NA/Pins 13 to 17):** VID Programming Inputs. These are logic inputs that set the output voltage at side 1 to a preprogrammed value (see Table 1). VID4 is the MSB, VID0 is the LSB. The codes selected by the VID*n* inputs correspond to the Intel Mobile VID specification. Each VID*n* pin includes an on-chip 40k $\Omega$  pull-up resistor in series with a diode (see Block Diagram). The LTC1702 does not include VID pins.

$V_{CC}$  (Pin 13/18): Power Supply Input. All internal circuits except the output drivers are powered from this pin.  $V_{CC}$  should be connected to a low noise power supply voltage between 2.7V and 7V, and should be bypassed to SGND with at least an 0.1µF capacitor in close proximity to the LTC1702/LTC1703.

**FB2 (Pin 14/19):** Controller 2 Feedback Input. FB2 should be connected through a resistor divider to  $V_{OUT2}$  to set the output voltage. The loop compensation network for controller 2 also connects to FB2. The FB2 pin on the LTC1703 is completely independent from the VID programming circuitry and works in the same manner as FB1 and FB2 on the LTC1702.

**COMP2 (Pin 15/20):** Controller 2 Loop Compensation. See COMP1.

RUN/SS2 (Pin 16): Controller 2 Run/Soft Start. See RUN/SS1.

**FAULT (Pin 17/22):** Output Overvoltage Fault (Latched). The FAULT pin is an open-drain output with an internal  $10\mu$ A pull-up. If either regulated output voltage rises more than 15% above its programmed value, for more than 10 $\mu$ s, the FAULT output will go high, the entire LTC1702/LTC1703 will be disabled, and both BG pins will go high, turning on the bottom MOSFET switches and pulling down the high output voltage. The LTC1702/LTC1703 will remain latched in this state until the power is cycled. When FAULT mode is active, the FAULT pin will be pulled up with an internal 10 $\mu$ A current source. Tying FAULT directly to PGND will disable FAULT mode and will cause the LTC1702/LTC1703 to ignore overvoltage faults.

**PWRGD2 (Pin 18/NA):** Controller 2 Power Good. See PWRGD1. The LTC1703 does not have PWRGD pins.

**PGND (Pin 19/23):** Power Ground. The BG*n* drivers return to this pin. Connect PGND to a high current ground node in close proximity to the sources of external MOSFETs, M21 and M22, and the  $V_{IN}$  and  $V_{OUT}$  bypass capacitors.

SW2 (Pin 20/24): Controller 2 Switching Node. See SW1.

TG2 (Pin 21/25): Controller 2 Top Gate Drive. See TG1.

BG2 (Pin 22/26): Controller 2 Bottom Gate Drive. See BG1.

**BOOST2 (Pin 23/27):** Controller 2 Top Gate Driver Supply. See BOOST1.

I<sub>MAX2</sub> (Pin 24/28): Controller 2 Current Limit Set. See I<sub>MAX1</sub>.

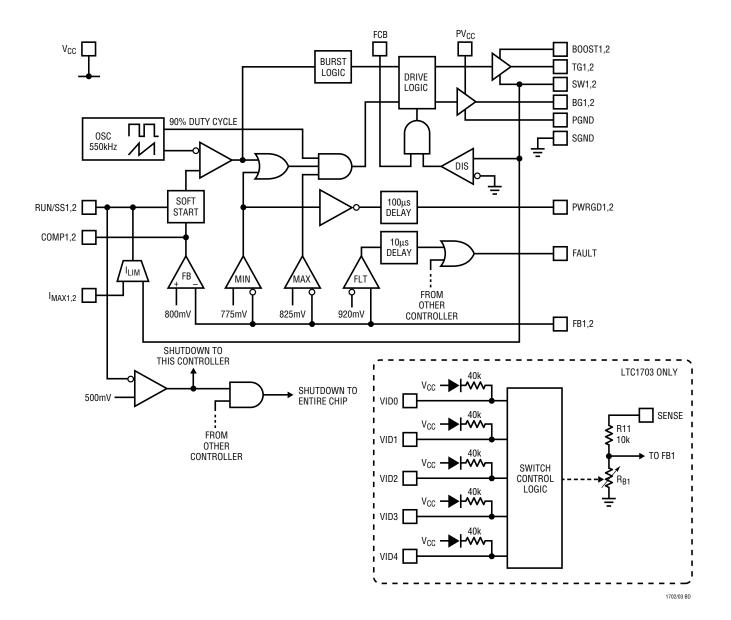

## **BLOCK DIAGRAM**

### VID PROGRAMMING CODES

| Table 1. VID Inputs and Corresponding Output Voltage |      |       |       |       |       |                   |

|------------------------------------------------------|------|-------|-------|-------|-------|-------------------|

| CODE                                                 | VID4 | VID3  | VID2  | VID1  | VIDO  | V <sub>OUT1</sub> |

| 00000                                                | GND  | GND   | GND   | GND   | GND   | 2.00V             |

| 00001                                                | GND  | GND   | GND   | GND   | Float | 1.95V             |

| 00010                                                | GND  | GND   | GND   | Float | GND   | 1.90V             |

| 00011                                                | GND  | GND   | GND   | Float | Float | 1.85V             |

| 00100                                                | GND  | GND   | Float | GND   | GND   | 1.80V             |

| 00101                                                | GND  | GND   | Float | GND   | Float | 1.75V             |

| 00110                                                | GND  | GND   | Float | Float | GND   | 1.70V             |

| 00111                                                | GND  | GND   | Float | Float | Float | 1.65V             |

| 01000                                                | GND  | Float | GND   | GND   | GND   | 1.60V             |

| 01001                                                | GND  | Float | GND   | GND   | Float | 1.55V             |

| 01010                                                | GND  | Float | GND   | Float | GND   | 1.50V             |

| 01011                                                | GND  | Float | GND   | Float | Float | 1.45V             |

| 01100                                                | GND  | Float | Float | GND   | GND   | 1.40V             |

| 01101                                                | GND  | Float | Float | GND   | Float | 1.35V             |

| 01110                                                | GND  | Float | Float | Float | GND   | 1.30V             |

| 01111                                                | GND  | Float | Float | Float | Float | 1.25V             |

#### CODE VID4 VID3 VID2 VID1 VIDO V<sub>OUT1</sub> GND 10000 GND GND GND 1.275V Float 10001 GND GND GND Float 1.250V Float 1.225V 10010 Float GND GND Float GND 10011 GND Float Float GND Float 1.200V 10100 Float GND Float GND GND 1.175V 10101 Float GND Float GND Float 1.150V 10110 Float GND Float Float GND 1.125V 10111 GND Float 1.100V Float Float Float 11000 Float GND GND GND 1.075V Float 11001 GND GND 1.050V Float Float Float 11010 Float Float GND Float GND 1.025V 11011 Float Float GND Float Float 1.000V 11100 GND GND Float Float Float 0.975V 11101 Float GND Float 0.950V Float Float 0.925V 11110 Float Float Float Float GND 11111 Float Float Float Float Float 0.900V

### **APPLICATIONS INFORMATION**

The LTC1702/LTC1703 are dual, step-down (buck), voltage mode feedback synchronous switching regulator controllers. The LTC1702 has two adjustable outputs, while the LTC1703 adds digital output voltage control to side 1. Both parts are designed to operate from a low voltage input supply (7V maximum) and provide high power, high efficiency, precisely regulated output voltages. Several features make the LTC1702/LTC1703 particularly suited for microprocessor supply regulation. Output regulation is extremely tight, with DC line and load regulation and initial accuracy better than 1%, and total regulation including transient response inside of 3% with a properly designed circuit. The 550kHz switching frequency allows the use of physically small, low value external components without compromising performance. The 800mV internal reference allow regulated output voltages as low as 800mV.

The LTC1702/LTC1703 synchronous switching logic can transition automatically into discontinuous and Burst Mode operation, maximizing efficiency with light loads. An onboard overvoltage (OV) fault flag indicates when an OV fault has occurred. The OV flag can be set to latch the device off when an OV fault has occurred, or to automatically resume operation when the fault is removed. The LTC1702 also includes a Power Good output for each channel to indicate when the output voltage is in regulation.

The LTC1702/LTC1703 run from low input voltages and generate two lower output voltages at very high current. Their strengths are small size, peerless regulation and transient response and high efficiency. This combination makes it ideal for providing multiple low voltage logic supplies to microprocessors or high density ASICs in systems using a "2-step" regulation architecture. often used in portable and advanced desktop computers.

#### 2-Step Conversion

"2-step" architectures use a primary regulator to convert the input power source (batteries or AC line voltage) to an intermediate supply voltage, often 5V. This intermediate voltage is then converted to the low voltage, high current supplies required by the system using a secondary requlator-the LTC1702/LTC1703. 2-step conversion eliminates the need for a single converter that converts a high input voltage to a very low output voltage-often an

### **APPLICATIONS INFORMATION**

awkward design challenge. It also fits naturally into systems that continue to use the 5V supply to power portions of their circuitry, or have excess 5V capacity available as newer circuit designs shift the current load to lower voltage supplies.

Each regulator in a typical 2-step system maintains a relatively low step-down ratio (5:1 or less), running at high efficiency while maintaining a reasonable duty cycle. In contrast, a regulator taking a single step from a high input voltage to a 1.xV or 2.xV output must run at a very narrow duty cycle, mandating trade-offs in external component values and compromising efficiency and transient response. The efficiency loss can exceed that of using a 2-step solution. Further complicating the calculation is the fact that many systems draw a significant fraction of their total power off the 5V supply, not the low voltage supply. 2-step solutions using the LTC1702/LTC1703 usually match or exceed the total system efficiency of 1-step solutions, and provide the additional benefits of improved transient response, reduced PCB area and simplified power trace routing.

2-step regulation can buy advantages in thermal management as well. Power dissipation in the LTC1702/LTC1703 portion of a 2-step circuit is lower than it would be in a typical 1-step converter, even in cases where the 1-step converter has higher total efficiency than the 2-step system. In a typical microprocessor core supply regulator, for example, the regulator is usually located right next to the CPU. In a 1-step design, all of the power dissipated by the core regulator is right there next to the hot CPU, aggravating thermal management. In a 2-step LTC1702/LTC1703 design, a significant percentage of the power lost in the core regulation system happens in the 5V supply, which is usually away from the CPU. The power lost to heat in the LTC1702/LTC1703 section of the system is relatively low, minimizing the heat near the CPU.

#### Fast Transient Response

The LTC1702/LTC1703 use an internal 25MHz GBW op amp as an error amplifier. This allows the compensation network to be designed with several poles and zeros in a more flexible configuration than a typical  $g_m$  feedback amplifier. The high bandwidth of the amplifier, coupled

with the high 550kHz switching frequency and the low values of the external inductor and output capacitor, allow very high loop crossover frequencies. The low inductor value is the other half of the equation—with a typical value under  $1\mu$ H, the inductor allows very fast di/dt slew rates. The result is superior transient response compared with conventional solutions.

#### **High Efficiency**

The LTC1702/LTC1703 use a synchronous step-down (buck) architecture, with two external N-channel MOSFETs per output. A floating topside driver and a simple external charge pump provide full gate drive to the upper MOSFET. The voltage mode feedback loop and MOSFET  $V_{DS}$  current limit sensing remove the need for an external current sense resistor, eliminating an external component and a source of power loss in the high current path. Properly designed circuits using low gate charge MOSFETs are capable of efficiencies exceeding 90% over a wide range of output voltages and currents.

#### LTC1703 VID Programming

The LTC1703 includes an onboard feedback network that programs the output voltage at side 1 in accordance with the Intel Mobile VID specification (Table 1). The network includes a 10k resistor (R11) connected from SENSE to FB1, and a variable value resistor (R<sub>B1</sub>) from FB1 to SGND, with the value set by the digital code present at the VID4  $\sim$  VID0 pins. SENSE should be connected to V<sub>OUT1</sub> to allow the network to monitor the output voltage. No additional feedback components are required to set the output voltage at controller 1, although loop compensation components are still required. Each VID*n* pin includes an internal 40k pull-up resistor, allowing it to float high if left unconnected. The pull-up resistors are connected to V<sub>CC</sub> through diodes (see Block Diagram), allowing the VID*n* pins to be pulled above V<sub>CC</sub> without damage.

Note that codes 01111 and 11111, defined by Intel to indicate "no CPU present," do generate output voltages at  $V_{OUT1}$  (1.25V and 0.9V, respectively). Note also that controller 2 on the LTC1703 is not connected to the VID circuitry, and works in exactly the same manner as the LTC1702.